|

ELECTRONICA

DIGITAL

LABORATORIO

N° 05

CIRCUITOS

CONTADORES CON

FLIP FLOPS

|

Alumno(s)

|

Nota

|

|

Mamani Abarca Jeanlu Manuel

|

||

Lanchipa Maldonado Alvaro

|

||

Grupo

|

A

|

|

Ciclo 4C4

|

Electrotecnia Industrial – Electrónica

Digital

|

|

Fecha de entrega

|

||

I. CAPACIDAD TERMINAL

·

Identificar las aplicaciones de la Electrónica

Digital.

·

Describir el funcionamiento de las unidades y

dispositivos de almacenamiento de información.

·

Implementar circuitos de lógica combinacional y

secuencial.

II. COMPETENCIA ESPECIFICA DE

LA SESION

·

Implementación de circuitos monoestables.

·

Implementación de circuitos contadores con Flip Flops JK.

·

Utilizar un SIMULADOR para comprobar el comportamiento de los mismos.

III.

CONTENIDOS A TRATAR

·

Circuitos Monoestables

·

Circuitos Contadores Ascendentes y Descendentes.

·

Aplicaciones con circuitos contadores.

IV. RESULTADOS

·

Diseñan sistemas eléctricos y los implementan

gestionando eficazmente los recursos materiales y humanos a su cargo.

V. MATERIALES Y EQUIPO

·

Entrenador para Circuitos Lógicos

·

PC con Software de simulación.

·

Guía de Laboratorio. El trabajo se desarrolla de manera GRUPAL.

VI. REPASO DEL LABORATORIO ANTERIOR

·

Diseño de circuitos sumadores y decodificadores

VII.

FUNDAMENTO TEÓRICO

·

Revise los siguientes

enlaces:

·

CIRCUITOS MONOESTABLES:

·

CIRCUITOS CONTADORES

CON FLIP FLOPS:

TAREAS GUIADAS DENTRO DEL LABORATORIO:

1. Determine

la Ecuación Lógica y la Tabla de Verdad del circuito mostrado.

2. Compruebe

en simulación el comportamiento de los circuitos mostrados.

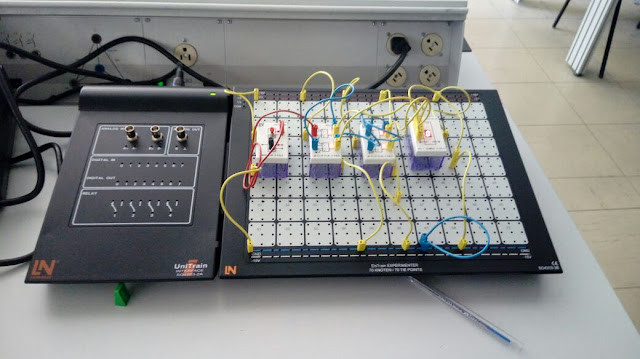

3. Armar circuito en el ENTRENADOR y verificar resultados.

4. Conecte

4 flip flops de la forma mostrada para formar un CONTADOR, compruebe su

funcionamiento implementando de forma física.

5. Finalmente

conecte al contador previo el DISPLAY DE 7 SEGMENTOS con decodificador incluido

para ver el incremento de los números. Utilizar los bloques mostrados:

6. LABORATORIO

6.1 Armado del circuito ascendente en Proteus

6.2 Armado del circuito descendente en Proteus

Armado del circuito ascendente

Armado del circuito descendente

Video Evidencia

7.

CONTENIDO DEL INFORME EN EL BLOG:

a.

Teoría de LATCHES y FLIP FLOPS

b. Observaciones y conclusiones. ¿Qué he aprendido de esta experiencia? (en modo texto)

b. Observaciones y conclusiones. ¿Qué he aprendido de esta experiencia? (en modo texto)

Latch

Un latch (Lat Memori Inglet) es un circuito electrónico

usado para almacenar información en sistemas lógicos asíncronos. Un latch puede

almacenar un bit de información. Los latches se pueden agrupar, algunos de

estos grupos tienen nombres especiales, como por ejemplo el 'latch quad' (que

puede almacenar cuatro bits) y el 'latch octal' (ocho bits). Los latches pueden

ser dispositivos biestables asíncronos que no tienen entrada de reloj y cambian

el estado de salida solo en respuesta a datos de entrada, o bien biestables

síncronos por nivel, que cuando tienen datos de entrada, cambian el estado de

salida sólo si lo permite una entrada de reloj.

RC Latch

Los latches a diferencia de los conectores no necesitan una

señal de reloj para su funcionamiento.

El latch lógico más simple es el RS, donde R y S permanecen

en estado 'reset' y 'set'. El latch es construido mediante la interconexión

retroalimentada de puertas lógicas NOR (negativo OR), o bien de puertas lógicas

NAND (aunque en este caso la tabla de verdad tiene salida en lógica negativa

para evitar la incongruencia de los datos). El bit almacenado está presente en

la salida marcada como Q.

Se pueden dar las siguientes combinaciones de entrada: set a

1 y reset a 0 (estado 'set'), en cuyo caso la salida Q pasa a valer 1; set a 0

y reset a 0 (estado 'hold'), que mantiene la salida que tuviera anteriormente

el sistema; set a 0 y reset a 1 (estado 'reset'), en cuyo caso la salida Q pasa

a valer 0; y finalmente set a 1 y reset a 1, que es un estado indeseado en los

biestables de tipo RS, pues provoca oscilaciones que hacen imposible determinar

el estado de salida Q.

Esta situación indeseada se soluciona con los biestables

tipo JK, donde se añade un nivel más de retroalimentación al circuito, logrando

que dicha entrada haga conmutar a las salidas, denominándose estado de

'toggle'.

Flip-flops

Los circuitos secuenciales son aquellos en los cuales su salida depende de la entrada presente y pasada. Dentro de estos circuitos se tienen a los Flip-Flops.

Los Flip-Flops son los dispositivos con memoria mas comúnmente utilizados. Sus características principales son:

1. Asumen solamente uno de dos posibles estados de salida.

2. Tienen un par de salidas que son complemento una de la otra.

3. Tienen una o mas entradas que pueden causar que el estado del Flip-Flop cambie.

A continuación se describirán 4 tipos de Flip-Flops.

Flip-Flop

S-R (Set-Reset)

La siguiente figura muestra una forma posible de implementar

un Flip-Flop S-R. Utiliza dos compuertas NOR. S y R son las entradas, mientras

que Q y Q’ son las salidas (Q es generalmente la salida que se busca

manipular).

Como existen varias formas de implementar un Flip-Flop S-R

(y en general cualquier tipo de Flip-Flop) se utilizan diagramas de bloque que representen

al Flip-Flop. El siguiente diagrama de bloque representa un FF S-R. Nótese que

ahora, por convención, Q se encuentra en la parte superior y Q’ en la

inferior.

Para describir el funcionamiento de un FF se utilizan las

llamadas Tablas de Estado y las Ecuaciones Características. La siguiente tabla

muestra la tabla de estado para un FF S-R.

Como encabezado de las columnas tenemos las entradas S y R,

y una de las salidas Q. La salida Q es la salida que en un tiempo t se puede

detectar en el FF, es decir, es la salida en el tiempo actual. Q+ es la salida

en el tiempo , una vez que se ha

propagado la señal en el circuito (recuerde que los FF tienen un componente de

retroalimentación.) Por lo tanto , es

decir, es la salida que tendrá Q en el futuro – una vez que se haya realizado

la propagación.

Si analizamos la tabla de estado, vemos que para si S = 0, R

= 0 y Q = 0 ó 1, la salida futura de Q (Q+) será siempre lo que se tenía antes

de la propagación. A este estado (S = 0, R = 0) se le conoce por tanto como

estado de memoria.

Viendo ahora el caso S = 0, R = 1, se aprecia que siempre Q+

= 0 sin importar el valor de Q antes de la propagación, es decir, se hace un

reset de Q. Si por el contrario, se tiene S = 1, R = 0, entonces Q+ = 1 en

ambos casos, por tanto se hace un set de Q.

Finalmente, nótese que la combinación S = 1, R = 1 no es

valida en el FF S-R. La razón es que dicho estado vuelve inestable al circuito

y, como una de las características de todo FF es que el estado es estable, al

usar dicha combinación se esta violando este principio de los FF.

Ahora, si se mapea la información de la tabla de estado del

FF S-R en un mapa de Karnaugh, se obtiene la siguiente ecuación

característica: . Esta ecuación describe

también el funcionamiento. Nos dice que Q+ será 1 siempre y cuando se haga un

set del FF o el reset no esta activado y la salida tiene un 1 en ese momento.

Flip-Flop T

El Flip-flop T cambia de estado en cada pulso de T. El pulso

es un ciclo completo de cero a 1. Las

siguientes dos figuras muestran el diagrama de bloque y una implementación del

FF T mediante un FF S-R y compuertas adicionales.

Nótese que en la implementación del FF T, las dos entradas

del FF S-R están conectadas a compuertas AND, ambas conectadas a su vez a la

entrada T. Además, la entrada Q esta conectada a R y Q’ a S. Esta conexión es

así para permitir que el FF S-R cambié de estado cada que se le mande un dato a

T. Por ejemplo, si Q = 1 en el tiempo actual, eso significa que Q’ = 0, por lo

tanto, al recibir T el valor de 1, se pasaran los valores de R = 1 y S = 0 al

FF S-R, realizando un reset de Q.

Flip-Flop J-K

La siguiente tabla muestra el comportamiento del FF T y del FF S-R en cada pulso

de T:

El flip-flop J-K es una mezcla entre el flip-flop S-R

y el flip-flop T. Esto ocurre de la siguiente manera:

- En J=1,

K=1 actúa como Flip-flop T

- De otra forma, actúa como flip-flop S-R

El siguiente diagrama de bloque es el perteneciente el

FF J-K:

Una implementación tentativa de un FF J-K a partir de

un FF S-R sin reloj es la siguiente:

La tabla de estado aparece a continuación. Note que es muy

parecida a la del FF S-R solo que ahora los estados de J=1 y K=1 sí son

validos.

Flip-Flop D

(Delay)

El flip-flop D es uno

de los FF más sencillos. Su función es dejar pasar lo que entra por D, a la

salida Q, después de un pulso del reloj. Es, junto con el FF J-K, uno de los

flip-flops más comunes con reloj. Su tabla de estado se muestra a continuación:

De la tabla se infiere que la ecuación característica para

el FF D es: Q+= D. El siguiente diagrama de bloques representa este flip-flop.

Observaciones y Conclusiones

Gracias

a este laboratorio conocimos el funcionamiento básico de un Latches y un Flip-Flop,

además de contar con el material adecuado para cada experiencia del laboratorio

aprendimos a construir nuestro propio circuito contador de manera descendente y

ascende utilizando nuestra lógica y el software Proteus.

En

plena experiencia del laboratorio notamos como el desplaye que utilizamos solo

llegaba hasta el número 9, de ahí asignaba a los otros números hasta el 15 las

primeras letras de abecedario.

Se logró

aplicar los conocimientos aprendidos de Fli-Flop y Latches en la creación de

los dos circuitos, el ascendente tubo un cableado fácil y corto, y el

descendente se complicó un poco pero al final se logró simularlo y armarlo.

Con todo lo aprendido comprendimos como es que una calculadora, reloj, carteles, etc funcionan. Todos tienen como base el principio del Flip - Flop y Latches.

Integrantes

-Mamani Abarca Jeanlu Manuel

-Lanchipa Maldonado Alvaro

No hay comentarios:

Publicar un comentario